-

01-05 19:00...苹果A系列芯片的晶体管数量从A7的10亿个增长至A18Pro的200亿个。这一增长与芯片功能的扩展密切相关:A7仅配备了两个高性能核心和一个四集群GPU,而A18Pro则拥有两个高性能核心、四个能效核心、一个16核神经网络处理器(NPU)和一个六集群GPU。尽管芯片功能大幅增强,A系列的芯片尺寸(diesize)却保持... 1

-

12-25 23:50...火为人类祖先带来光明和温暖,开启文明篇章。火焰和白炽灯都是自发辐射的光源,它们通过燃烧或加热,使电子进入高能态,然后在真空零点能作用下,释放出光子,照亮世界。受激辐射则揭示了光与物质之间更为深刻的互动。当外来的光子经过处于激发状态的物质时,会引发物质释放出与入射光子完全相同的新光子。这种被“复制”出的光子,使得光束具有... 0

-

12-05 18:30...好多人老是喜欢猜来猜去,比如是不是撞墙了呀、Scaling还有没有效啊……有的时候我都被大家的猜测震惊到。为什么不直接看看进展曲线呢?在我看来,赌一个指数对抗另一个指数是个糟糕的选择。这么说吧,Scaling有三个关键:算力+数据+算法。它们之间没有固定的搭配比例,比如如果有更好的数据,可以少计算些;或者如果有更多的算... 0

-

11-14 20:40...晶体管是现代电子设备和集成电路中的基础元件,具有多种重要功能,包括放大和开关电信号。然而,受玻尔兹曼暴政这一基本物理限制的影响,硅基晶体管无法在低于一定电压的条件下工作,这无疑限制了其进一步提升性能,以及扩展适用范围。为打破这一瓶颈,团队利用由锑化镓和砷化铟组成的超薄半导体材料,研制出这款新型3D晶体管。该晶体管性能与... 1

-

10-23 12:50...团队使用普通的3D打印机和成本低廉、可生物降解的材料,打印了这些无半导体器件。虽然这些器件性能还不足以与传统半导体晶体管相比,但它们已能执行一些基本的控制任务,比如调节电动机的速度。这项新技术使用的能量较少,产生的废物也更少,不仅降低了生产成本,还减少了对环境的影响。实验过程中,团队发现掺杂铜纳米颗粒的聚合物细丝具有一... 0

-

09-02 23:10...有望用于设计集成度更高、功能更丰富的集成电路。相关成果以“一种基于载流子可控受激发射的热发射极晶体管”为题,15日发表于《自然》期刊上。近年来,随着晶体管尺寸不断缩小,其进一步发展在速度和功耗等方面面临着众多挑战,寻找具有新工作原理的晶体管已经成为制备高性能集成电路的关键。正如水龙头可以控制水管中的水流,晶体管可以控制... 2

-

-

08-26 13:20...芯片上的元件数量将以每年翻倍的速率增加。1975年,他将翻倍周期修改为两年。在这种增长节奏的推动下,人类先后进入了PC时代、互联网时代和AI时代。但功耗、内存、开关频率以及算力瓶颈等问题,正滞缓摩尔定律的前进。更为重要的是,摩尔定律受量子力学的限制,晶体管的尺寸正逼近物理极限。“当晶体管小到原子尺寸时,量子效应会发生作... 1

-

08-18 19:40...由中国科学院金属研究所刘驰、孙东明研究员和成会明院士主导,与任文才团队和北京大学张立宁团队合作使用石墨烯等低维材料,构建了一种既可以降低功耗、又具有“负电阻”等功能的热发射极晶体管,有望用于设计集成度更高、功能更丰富的集成电路。相关成果以“一种基于载流子可控受激发射的热发射极晶体管”为题,15日发表于《自然》期刊上。近... 2

-

08-09 16:10...这种材料具有卓越的绝缘性能,即使在厚度仅为1纳米时,也能有效阻止电流泄漏。相关成果8月7日发表于国际学术期刊《自然》。“二维集成电路是一种新型芯片,用厚度仅为1个或几个原子层的二维半导体材料构建,有望突破传统芯片的物理极限。但由于缺少与之匹配的高质量栅介质材料,其实际性能与理论相比尚存较大差异。”中国科学院上海微系统与... 2

-

08-04 20:30...假设一个D1芯片可以实现362teraflops,要达到100exaflops,特斯拉将需要超过27.6万个D1芯片,或者超过32万英伟达A100GPU。500亿晶体管,D1已投产2021年特斯拉AIDay上,D1芯片初次亮相,拥有500亿晶体管,只有巴掌大小。它具备了强大和高效的性能,能够快速处理各种复杂的任务。今年... 1

-

08-04 18:40...假设一个D1芯片可以实现362teraflops,要达到100exaflops,特斯拉将需要超过27.6万个D1芯片,或者超过32万英伟达A100GPU。500亿晶体管,D1已投产2021年特斯拉AIDay上,D1芯片初次亮相,拥有500亿晶体管,只有巴掌大小。它具备了强大和高效的性能,能够快速处理各种复杂的任务。今年... 1

-

08-01 11:40...海量数据的处理对芯片的算力和能量效率提出了严峻挑战。然而,高能效计算芯片的发展正遭遇芯片架构、晶体管性能两个重大瓶颈:传统的冯·诺依曼架构已经无法满足高速、高带宽的数据搬运和处理需求,未来的高能效运算芯片必须在硬件架构上进行革新,以适用于神经网络等模型的张量数据运算。同时,构建芯片的硅基互补金属氧化物半导体晶体管也处于... 2

-

-

07-13 15:30...利用光刻技术在全画幅尺寸芯片上集成了2700万个有机晶体管并实现了互连,集成度达到特大规模集成度水平。该成果日前以《基于光伏纳米单元的高性能大规模集成有机光电晶体管》为题发表于《自然·纳米技术》。随着现代信息科技的发展,功能芯片的集成密度越来越高,硅基芯片集成器件的密度已经超过每平方毫米2亿个晶体管。目前,集成电路芯片... 0

-

07-09 23:20...”陆建华说。智慧天网创新工程是多学科相互渗透、相互交叉的复杂系统工程,面临着人才培养周期长和技术更新迭代快等多重考验。3年多来,清华大学时刻牢记习近平总书记殷殷嘱托,以“科研创新成果与国家发展需要丝丝相扣”为指引,全力推进工程发展。——突破关键技术。项目团队攻克了星上处理交换模组化设计、捷变波束空时灵活控制、空间激光通... 1

-

10-18 21:10...而许多人工智能算法将迅速耗尽这些电池的电量。这种新型晶体管由二硫化钼和碳纳米管制成。它们可以通过电场不断重新配置,几乎可在瞬间处理人工智能驱动过程中的多个步骤。相比之下,作为微小电子开关的硅基晶体管一次只能执行一个步骤。这意味着一项需要100个硅基晶体管的人工智能任务,现在只需要一个可重构的晶体管就能完成,从而降低了能... 2

-

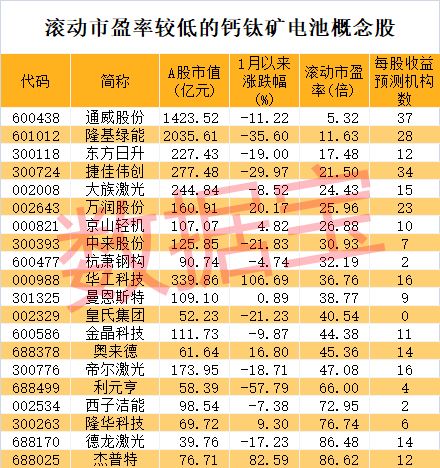

09-13 10:30...该团队成功开发出了缺陷更少的高质量P型钙钛矿半导体层。研究小组表示,他们再次成功开发出了世界上性能最好的晶体管,超越了去年的性能。钙钛矿电池产业化有望提速钙钛矿半导体具有很高的光吸收系数和载流子迁移率,使其在太阳能电池、光电探测器、发光二极管(LED)等器件中具有潜在的应用价值。钙钛矿电池是指利用钙钛矿型的有机金属卤化... 8

-

09-12 20:20...这枚镜头的焦段为85mm,最大光圈为2.8,采用了英寸传感器,最高可能可以支持高达10倍的光学变焦能力。在这段官网的文案介绍中,小编认为值得注意的点有以下几个,首先是“双层品体管的绝妙设计”。双层品体管设计是啥?通过查阅资料,小编发现意思是iPhone15ProMax的摄像头CMOS升级为了“双层晶体管像素堆叠式CMO... 5

-

09-02 22:00...150瓦功率放大器电路图:功率放大器电路设计:AB类放大器级的设计:晶体管的选择:这里所需的输出功率为150W。考虑到晶体管的功率耗散,我们假设所需功率约为200W。这里我们选择+/-50V双电源,即Vcc=50V,负载为8欧姆。为了提高电路效率,我们选择了一对达林顿晶体管-TIP142(NPN)和TIP147(PNP... 2

-

-

05-25 23:20...瑞典皇家理工学院和林雪平大学的研究团队在这方面取得了进展,首次成功地使用导电木头制造出了晶体管。这种晶体管不仅可以控制电流,而且还具有可降解、可持续、低成本等优点。最新研究成果已经发表在了《美国国家科学院院刊》(PNAS)上。瑞典林雪平大学有机电子实验室的高级副教授IsakEngquist说,“我们提出了一个前所未有的... 24

-

05-25 09:10...谢飚同步重点介绍了SonyExpo现场发布和展示的一系列新品,包括ZV系列新一代产品,超广角变焦Vlog相机ZV-1II,具备18-50mm广角镜头和增强防抖功能;98英寸超大规格X90L电视,搭载XR认知芯片以及一系列的前沿画质技术,配合多声道屏幕声场和3D环绕声场转换技术;新型空间现实显示屏ELF-SR2,无需佩戴... 19

-

05-05 23:40...三星电子在全球率先基于全环绕栅极(Gate-All-Around,GAA)晶体管结构量产了3纳米芯片。GAA架构是下一代代工微细加工工艺,是一项关键技术,可以改善静电特性,从而提高性能,降低功耗和优化芯片设计。三星表示,与之前的处理节点相比,3纳米GAA技术的性能提升了30%,能耗降低了50%,芯片面积减少了45%。三... 26

-

05-01 08:20...一扫N3的阴霾。▲负责生产3nm芯片的晶圆十八厂图片来自:台积电不过,鉴于此前大部分厂商都砍掉了N3的订单,让台积电此前巨额投入打了水漂,此时也影响到了自身5nm、7nm的产能和布局。为了让N3E顺利转型和量产,台积电针对N3E做了一点微小的调整。相对于初始的计划,N3E会使用更少的EUV光刻层,从25层缩减到21层,... 5

-

-

-

本页Url:

-

2025-01-22-17:33 GMT . 添加到桌面浏览更方便.

-